Las CPU Ryzen 9000 Desktop basadas en Zen 5 de AMD no proporcionaron la mejora de rendimiento que todos esperábamos. Si bien una de las razones de este desalentador resultado se puede atribuir a las optimizaciones deficientes para Windows 11, no es la única razón. El llamado «Core Parking» (que es quien deshabilita automáticamente los núcleos cuando no se necesitan con el fin de conseguir un ahorro energético) no está optimizado y es uno de los culpables que da como resultado un rendimiento más lento de lo ideal, supuestamente debido al software incompleto y la compatibilidad con BIOS.

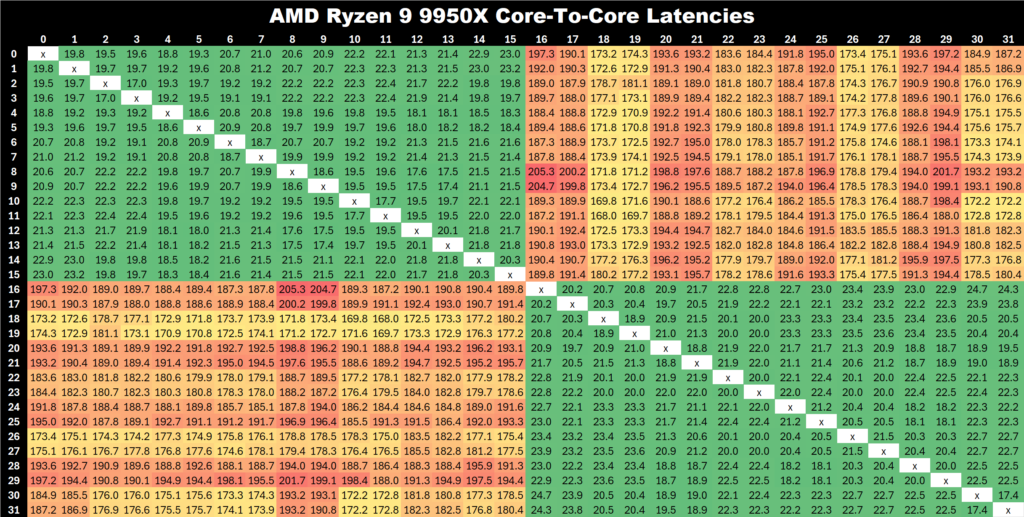

En la revisión de Anandtech del Ryzen 9 9950X , se descubrió que la CPU Zen 5 tenía una latencia entre CCD significativamente mayor en comparación con su predecesora. Esto se debe a que las CPU Zen 4 y Zen 5 comparten un diseño de matriz de E/S y de estructura infinita similar. Sin embargo, un informe reciente de Geekerwan en Bilibili (a través de @9950pro ) sugiere que AMD está trabajando para solucionar este problema a través de un futuro parche de BIOS.

La latencia entre CCD es la velocidad con la que se transfieren los datos o las instrucciones entre los dos CCD Zen 5 (Core Complex Dies) dentro de las CPU Ryzen 9000. Esta estructura se utiliza para la comunicación con múltiples chiplets, como CCD e IOD. Como Ryzen 9 9950X y Ryzen 9 9900X contienen dos CCD, y cada uno de ellos lleva 8 núcleos Zen 5, los programas que utilizan más de 8 núcleos necesitan que los datos se transfieran entre los CCD para una ejecución más rápida.

Desafortunadamente, el AMD Ryzen 9 9950X tiene casi el doble de latencia de CCD a CCD en comparación con el anterior. La latencia promedio entre CCD para Zen 5 es de 180 ns en comparación con los 76 ns del 7950X. Esto da como resultado una transferencia de datos más lenta entre los CCD, lo que resulta en un rendimiento multiproceso más lento de los esperado en algunas cargas de trabajo.

La mayor latencia entre CCD no se debe al diseño de la matriz, sino a las optimizaciones inacabadas y sin pulir de AMD en la BIOS y en la pila de software del chipset. Como sugiere el nuevo informe, AMD solucionará la alta latencia entre CCD mediante una actualización de la BIOS que debería implementarse en los próximos meses.

Con suerte, veremos algunas mejoras de rendimiento con la nueva actualización, pero aún no se conoce la fecha exacta de la actualización de la BIOS. Sin embargo, esta solución no afectará necesariamente al rendimiento en juegos, ya que la mayoría de los juegos no utilizan más de un CCD que contenga 8 núcleos. Solo en los programas que pueden utilizar más de 8 núcleos, la solución de latencia entre CCD puede resolver algunos problemas de rendimiento.

Ayer mismo, AMD anunció que incorporará optimizaciones de branch prediction, lo que dará como resultado una mejora del rendimiento. En conclusión, es evidente que AMD probablemente se apresuró a lanzar una serie Ryzen 9000 inacabada, que necesita más optimizaciones para proporcionar algunas mejoras generacionales significativas.