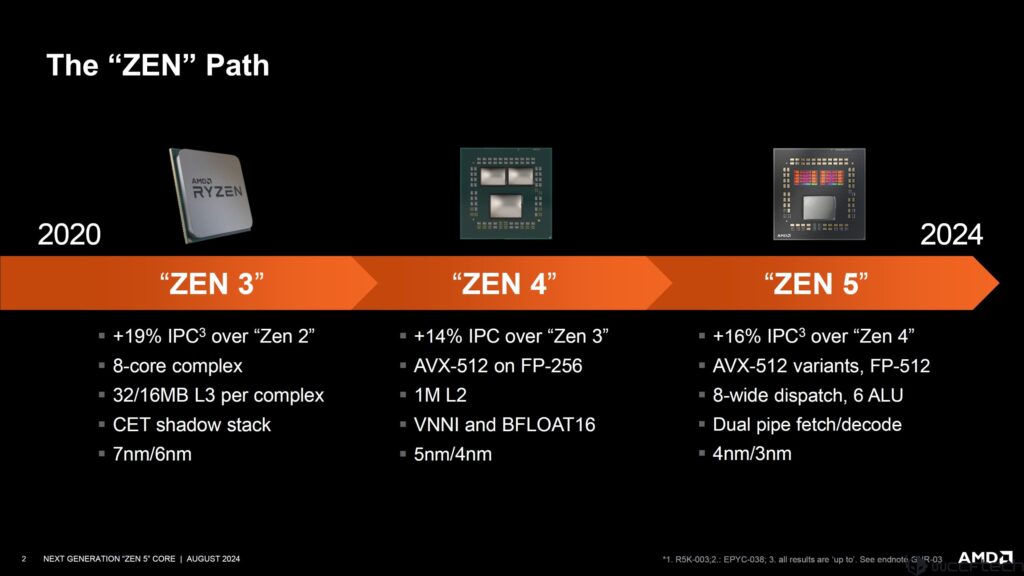

La arquitectura de núcleo Zen 1 de AMD se lanzó por primera vez en 2017 y, desde entonces, la empresa ha presentado cinco nuevas arquitecturas (Zen+, Zen 2, Zen 3, Zen 4, Zen 5). AMD comenzó la década con el lanzamiento de la arquitectura Zen 3, que trajo consigo una mejora del IPC del 19 %, un complejo de 8 núcleos y un aumento de los cachés L3 por CCX al tiempo que utilizaba las tecnologías de proceso de 7 nm/6 nm.

La compañía continuó con el lanzamiento de Zen 4, aportando otra mejora del 14% de IPC, instrucciones AVX-512 (FP-256), duplicando el caché L2 a 1 MB, soporte para VNNI/BFLOAT16 y utilizando la tecnología de proceso de 5 nm y 4 nm.

Este año, AMD presentó Zen 5, su última arquitectura de núcleo de alto rendimiento que ofrece un aumento del IPC del 16 % con variantes AVX-512 y FP-512, distribución de 8 núcleos, 6 ALU, búsqueda/decodificación de doble canal y uso de tecnología de 4 nm/3 nm. Hoy, AMD está profundizando en la arquitectura completa de su Zen 5 en Hot Chips.

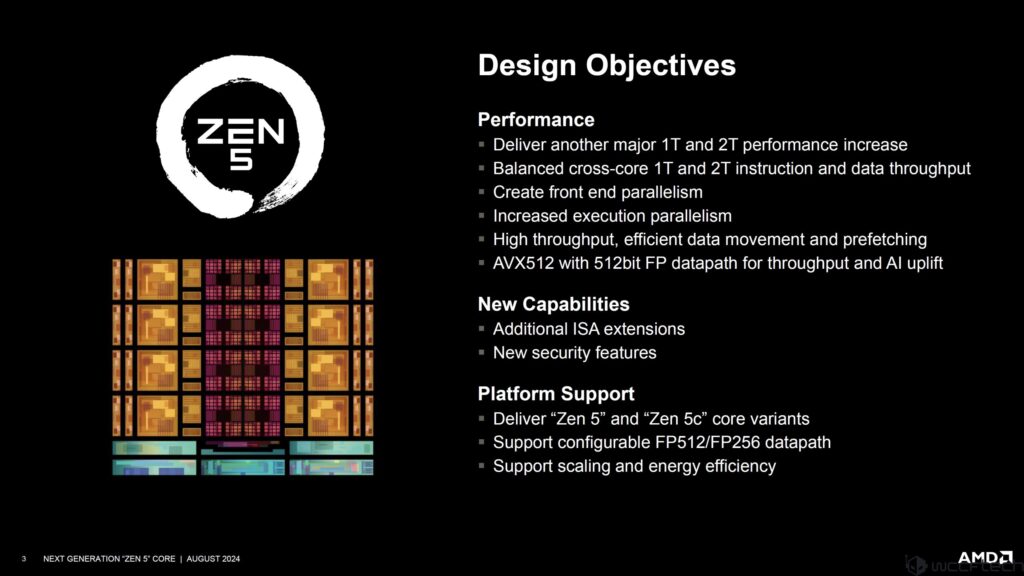

AMD comienza por indicar los objetivos de diseño para Zen 5. En términos de rendimiento, Zen 5 apunta a ofrecer otro importante aumento de rendimiento de 1T y NT, un equilibrado rendimiento de datos e instrucciones 1T/NT entre núcleos, crear paralelismo front-end, aumentar el paralelismo de ejecución, alto rendimiento, movimiento y precarga de datos eficientes, y compatibilidad con rutas de datos AVX512/FP512 para mejoras de rendimiento e IA. Al mismo tiempo, AMD quiere añadir nuevas capacidades, como extensiones ISA adicionales y nuevas funciones de seguridad, junto con un soporte de plataforma ampliado con sus variantes de núcleo Zen 5 y Zen 5C.

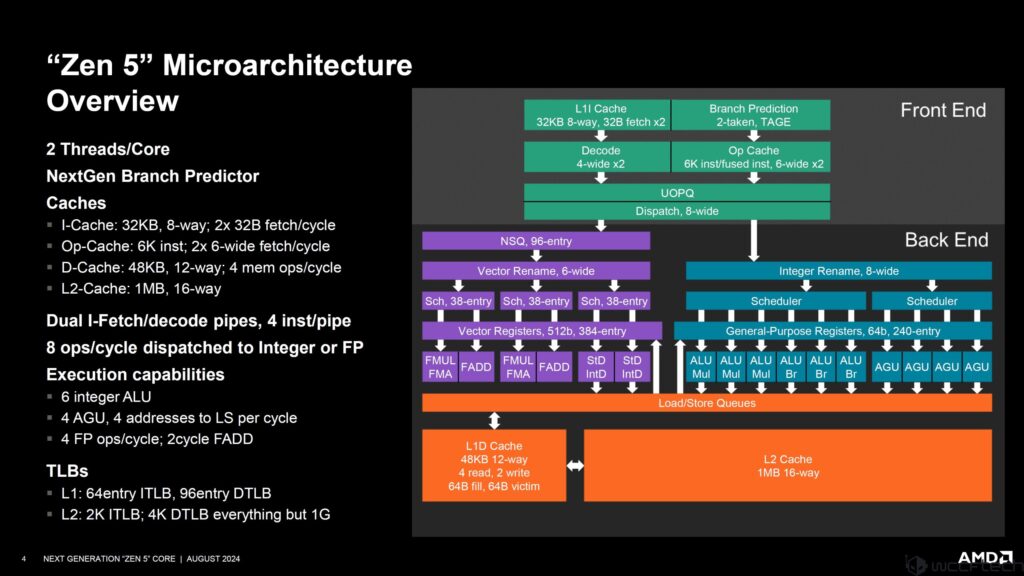

A continuación se muestra una descripción general de la arquitectura del núcleo Zen 5 de AMD:2 Threads/Core

NextGen Branch Predictor

Caches:

- I-Cache: 32KB, 8-way; 2x32B fetch/cycle

- Op-cache: 6K inst; 2x 6-wide fetch/cycle

- D-Cache: 48KB, 12-way; 4mem ops/cycle

- L2-Cache: 1MB, 16-way

Dual I-Fetch/decode pipes, 4 inst/pipe

8 ops/cycle dispatched to integer or FP

Execution capabilities:

- 6 Integer ALU

- 4 AGU, 4 addresses to LS per cycle

- 4 FP ops/cycle; 2cycle FADD

TLBs:

L2: 2K ITLBl 4K DTLB everything but 1G

L1: 64 entry ITLB, 96entry DTLB

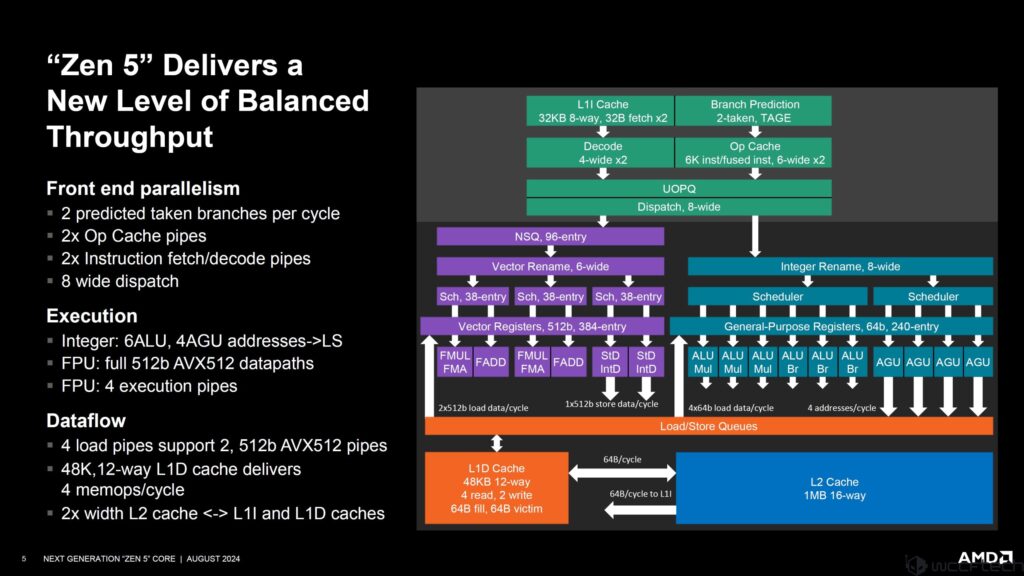

En cuanto a lo que ofrece el Zen 5 para proporcionar un rendimiento equilibrado, lo que estás viendo es:

Front End parallelism:

- 2 predicted token branches per cycle

- 2x Op cache pipes

- 2x instruction fetch/decode pipes

- 8 wide dispatch

Execution:

- Integer: 6ALU, 4AGU addresses->LS

- FPU: full 512b AVX512 datapaths

- FPU: 4 execution pipes

Dataflow:

- 4 load pipes support 2, 512b AVX512 pipes

- 48K, 12-way L1D cache delivers 4 memops/cycle

- 2x width L2 cache <-> L1I and L1D caches

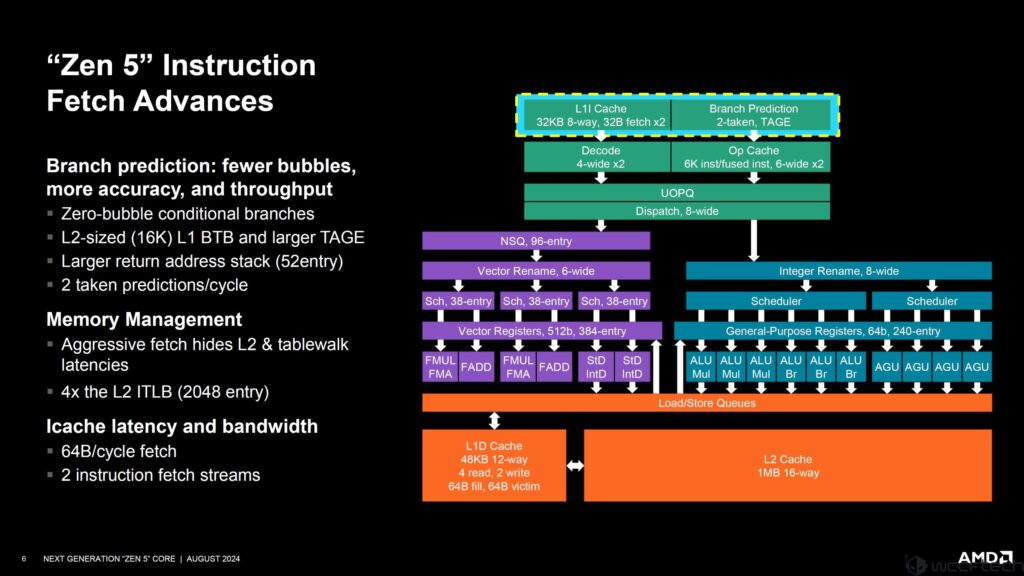

En términos de avances de Fetch, la arquitectura de núcleo Zen 5 de AMD ofrece:

Branch Prediction: fewer bubbles, more accuracy, and throughput

- Zero-bubble conditional branches

- L2-sized (16K) L1 BTB and larger TAGE

- Larger return addresses stack (52 entry)

- 2 taken predictions/cycle

Memory management:

- Aggressive fetch hides L2 & table walk latencies

- 4x the L2 ITLB (2048 entry)

Icache latency and bandwidth

- 64B/cycle fetch

- 2 instruction fetch streams

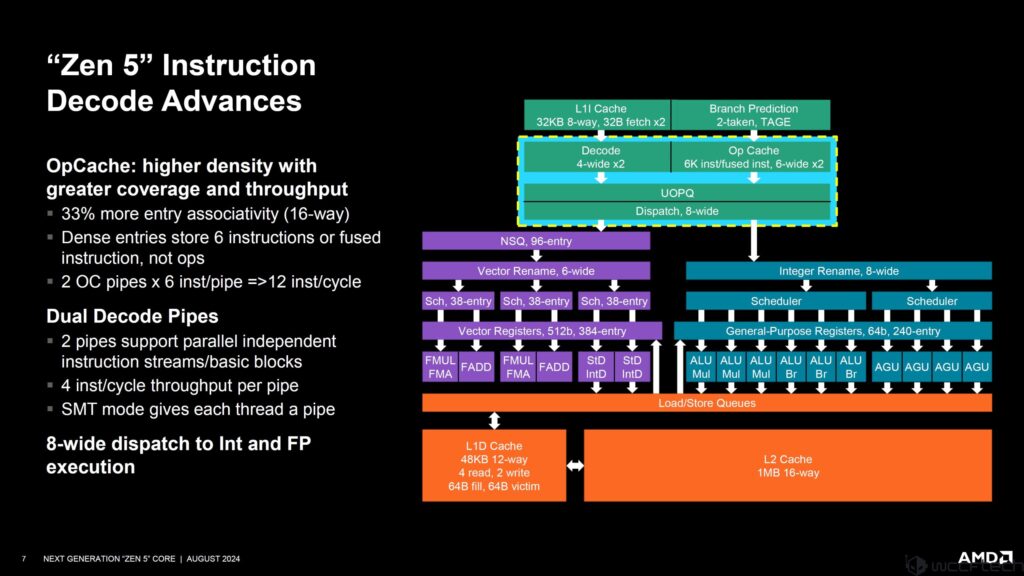

En términos de avances de decodificación, la arquitectura de núcleo Zen 5 de AMD ofrece:

Opcache: higher density with greater coverage and throughput

- 33% more entry associativity (16-way)

- Dense entries store 6 instructions or fused instructions, not ops

- 2 OC pipes x 6 inst/pipe -> 12 inst/cycle

Dual Decode Pipes

- 2 pipes support parallel independent instruction streams/basic blocks

- 4 inst/cycle throughput per pipe

- SMT mode gives each thread a pipe

8-wide dispatch to Int and FP execution

En términos de avances en ejecución, la arquitectura de núcleo Zen 5 de AMD ofrece:

In terms of Execution Advances, AMD’s Zen 5 core architecture offers:

8-wide dispatch, rename, retire

Integer scheduler advances

- Unified with age matrix

- More symmetry, simplifying pick

6 ALU with 3 multipliers, 3 branch units

4 AGU feed a wider LS with 4 memory addresses per cycle

Execution window growth

- Scheduler growth

- 240-entry physical register file

- ROB/retire queue 448/224 1T/2T entries

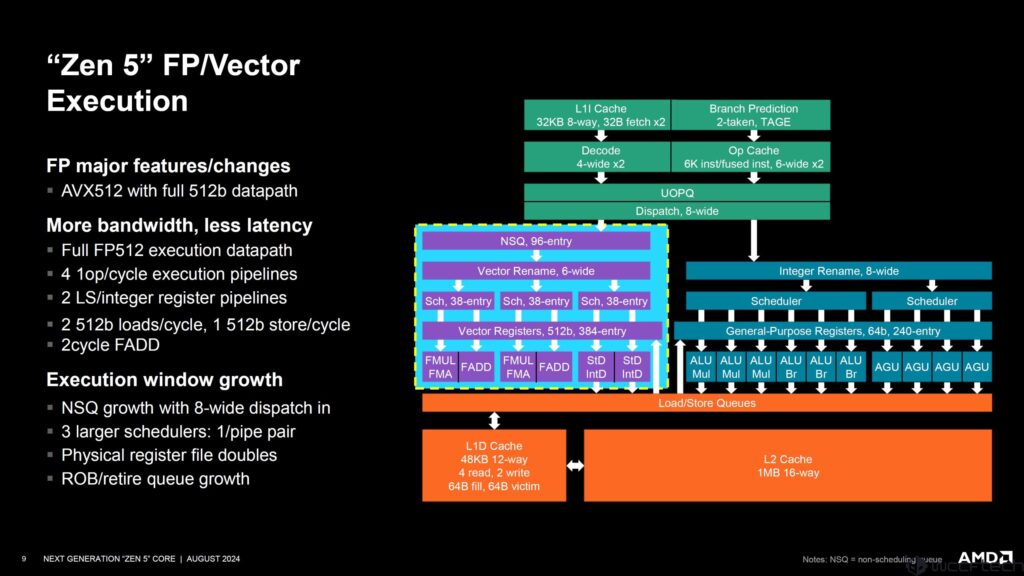

AMD también ha realizado cambios importantes en FP y ha añadido nuevas características como el mencionado AVX 512 con ruta de datos completa de 512b. Zen 5 ofrece más ancho de banda y menos latencia con 4 pipelines de ejecución de 1op/ciclo, 2 pipelines de registro entero/LS, 2 cargas de 512b/ciclo, 1 almacenamiento de 512b/ciclo y 2 FADD de ciclo. La ventana de ejecución también se ha ampliado con un despacho de 8 anchos en 3 programadores más grandes (1/par de pipelines) y el archivo de registro físico se ha duplicado.

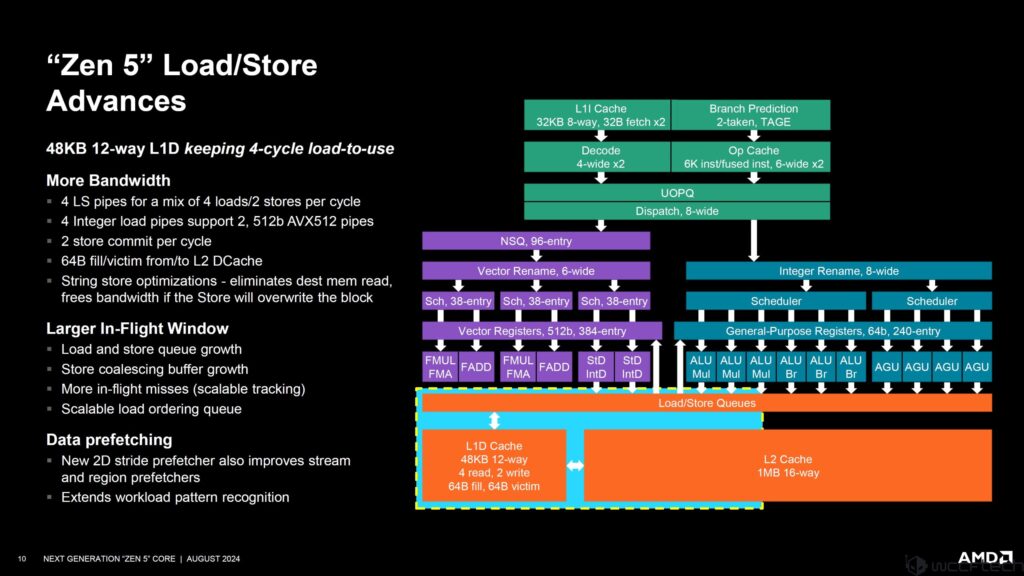

Por último, tenemos los avances de Carga y Almacenamiento que incluyen:

48KB 12-way L1D keeping 4-cycle load-to-use

More Bandwidth

- 4 LS pipes for a mix of 4 loads/2 stores per cycle

- 4 Integer load pipes support 2, 512b AVX512 pipes

- 2 store commit per cycle

- 64B fill/victim from/to L2 DCache

- String Store optimizations – eliminates dest mem read, frees bandwidth if the Store will overwrite the block

Larger In-Flight Window

- Load and Store queue growth

- Store coalescing buffer growth

- More in-flight misses (scalable tracking)

- Scalable load ordering queue

Data prefetching

- New 2D stride prefetcher also improves stream and region prefetchers

- Extends workload pattern recognition

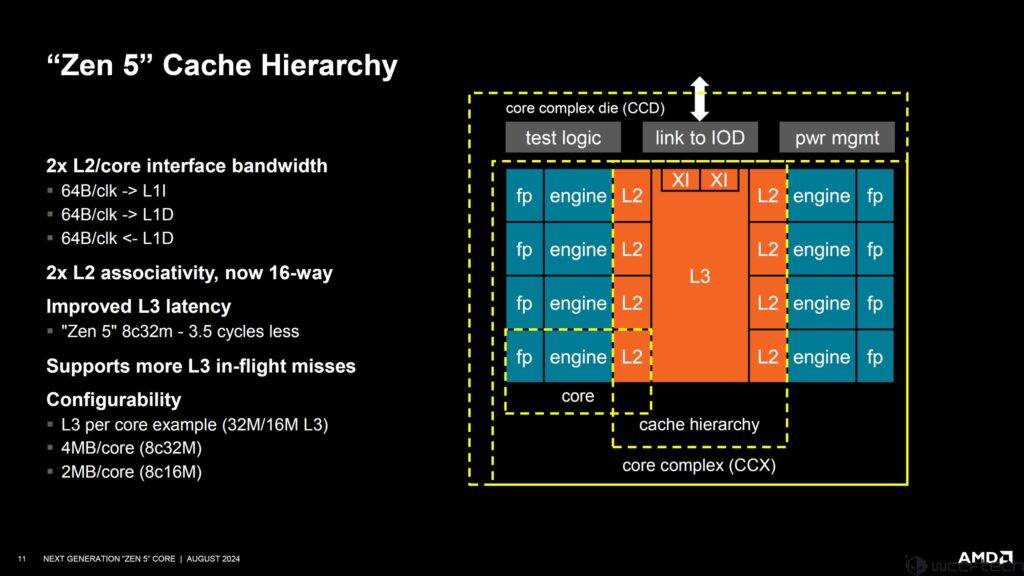

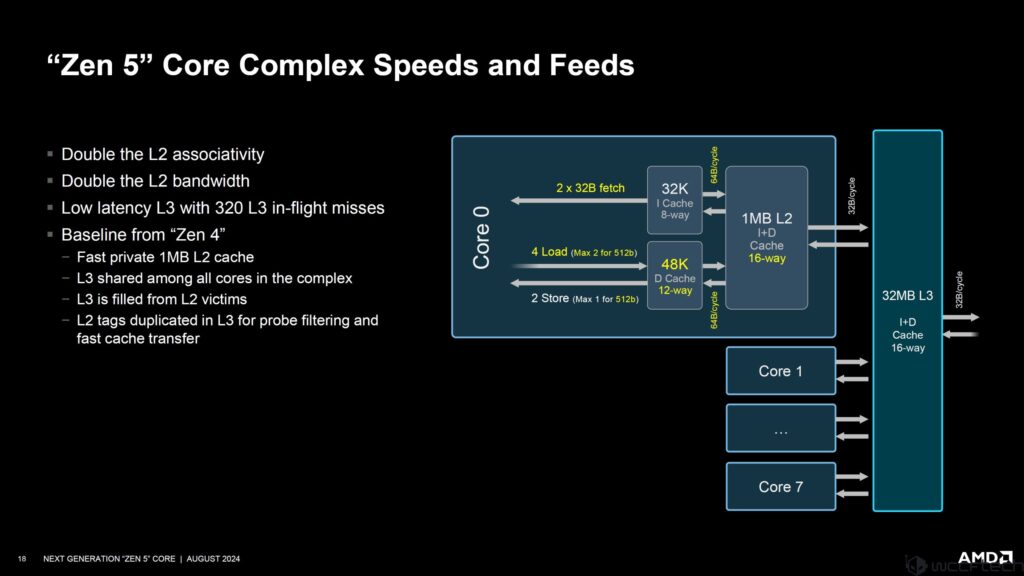

Pasando al caché, Zen 5 ha visto ciertas actualizaciones con el doble de ancho de banda de interfaz L2/núcleo con 64B/clk a L1 y L1D y desde L1D, 2x asociatividad L2 que ahora es de 16 vías y hace 3,5 ciclos menos, admite más fallas en vuelo L3 y las configuraciones incluyen 32/16 MB L3 (Zen 5 / Zen 5C), 4 MB por núcleo (Zen 5) y 2 MB por núcleo (Zen 5C).

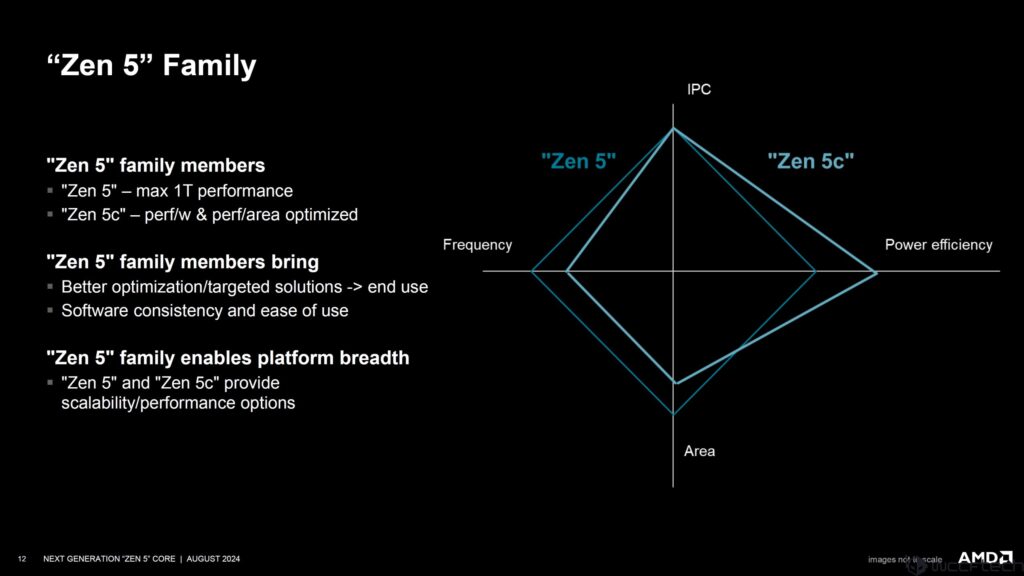

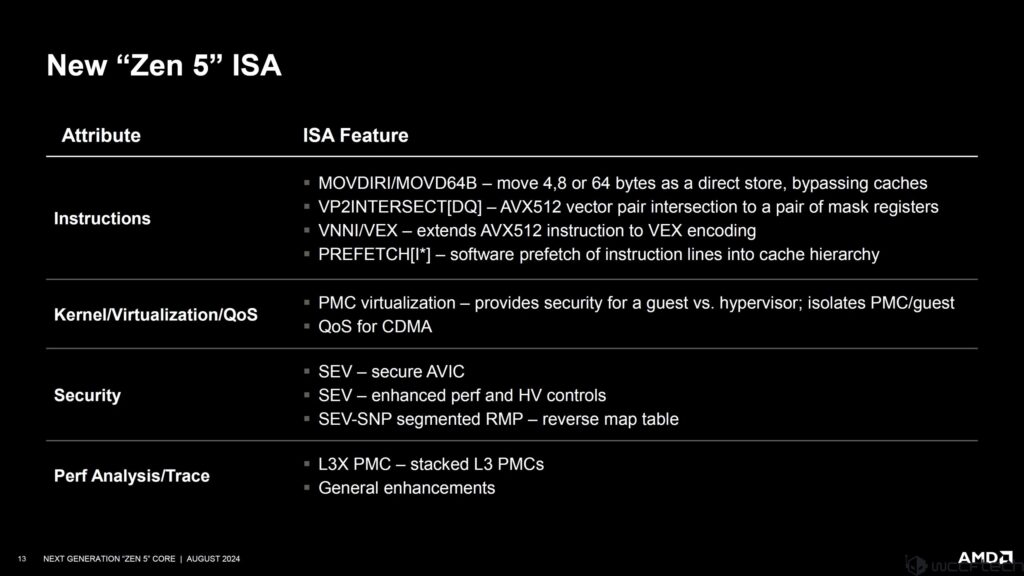

Hablando de las dos configuraciones, el núcleo Zen 5 está optimizado para un rendimiento máximo de 1T, mientras que el núcleo Zen 5C está orientado a plataformas optimizadas para rendimiento/área y rendimiento/w. Tanto Zen 5 como Zen 5C utilizan la misma ISA, que incluye lo siguiente:

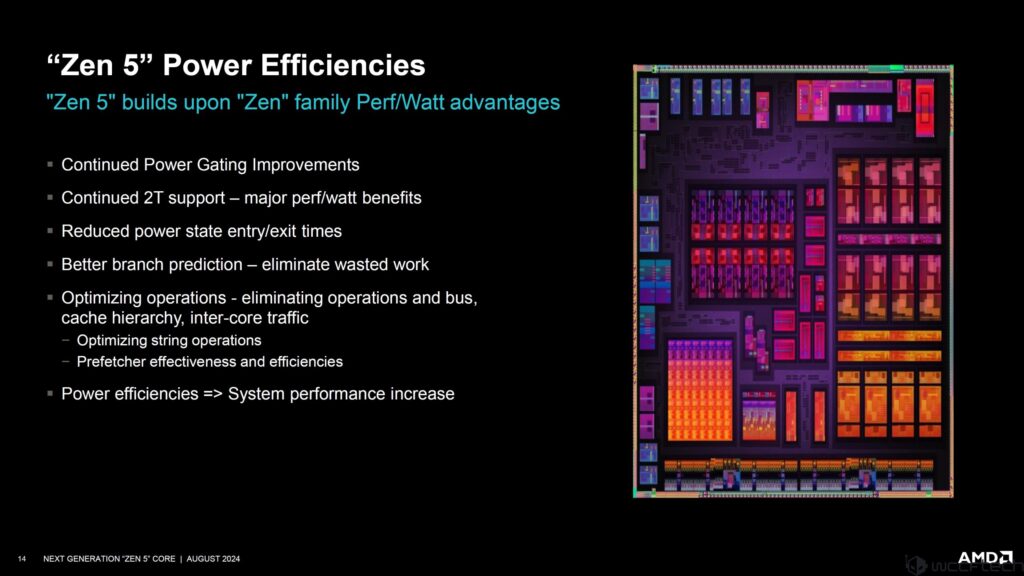

Para mejorar la eficiencia energética, AMD ha desarrollado Zen 5 desde cero y continúa desarrollando las mejoras de control de potencia y la compatibilidad con 2T (importantes beneficios de pref/watt). La arquitectura Zen 5 también presenta tiempos de entrada/salida de estado de potencia reducidos, mejor predicción de bifurcaciones para eliminar el trabajo innecesario y también optimiza las operaciones al eliminar el tráfico de bus, caché y entre núcleos a través de optimizaciones de operaciones de cadena y eficacia y eficiencia del prefetcher.

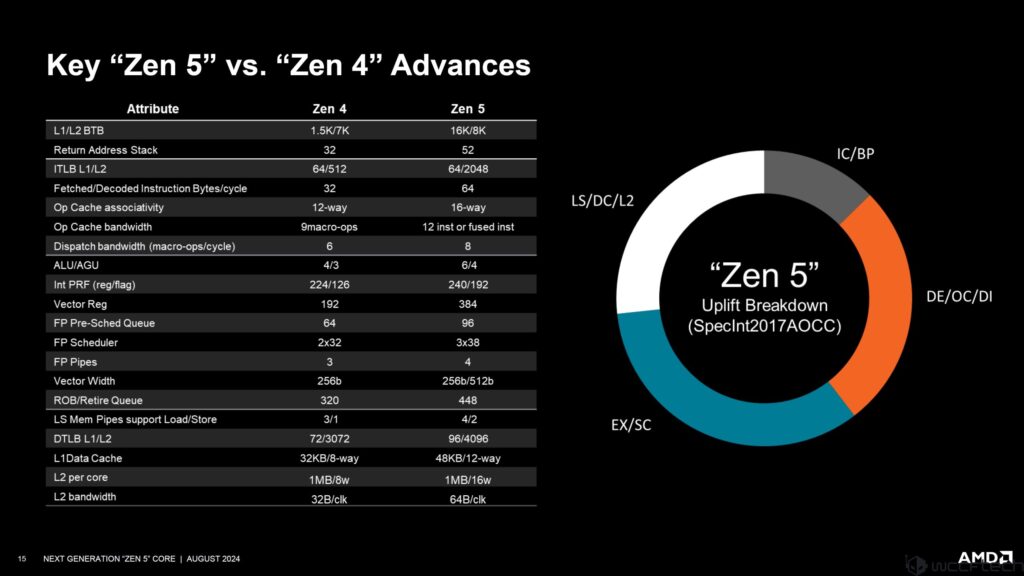

A continuación se presentan los avances clave logrados entre Zen 5 y Zen 4:

AMD también comparte las velocidades y los avances del complejo de núcleos Zen 5, que ofrece el doble de asociatividad L2, el doble de ancho de banda L2, L3 de baja latencia con 320 fallas en vuelo L3, un caché L2 rápido y privado (1 MB), L3 compartido entre todos los núcleos en el complejo, L3 lleno de víctimas L2 y etiquetas L2 duplicadas en L3 para filtrado de sondas y transferencia rápida de caché.

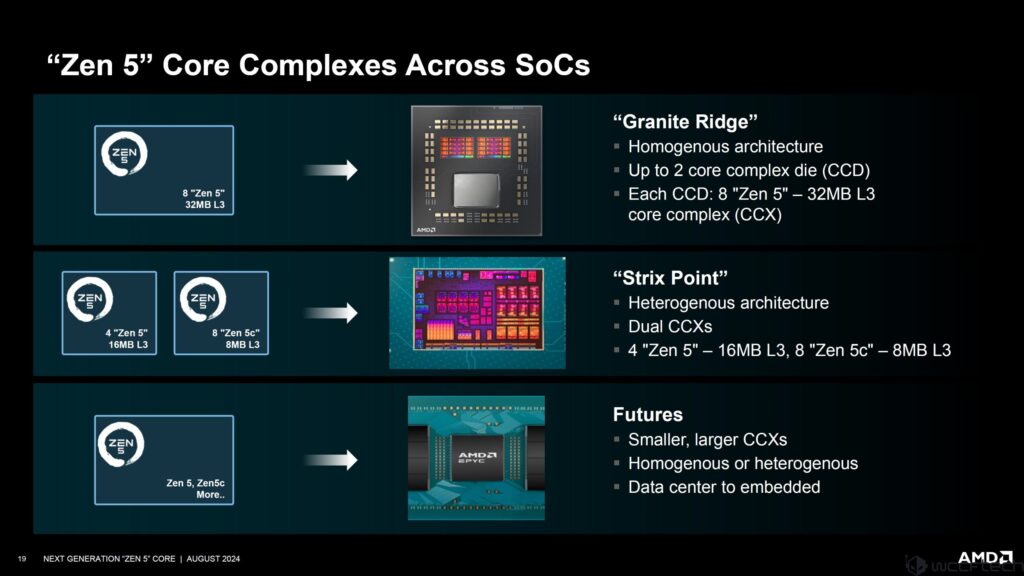

En cuanto a los productos, los complejos de núcleos Zen 5 de AMD o CCX se presentarán en primer lugar en tres rondas de productos. Estos incluyen las CPU de escritorio Ryzen 9000 «Granite Ridge», las CPU para portátiles Ryzen AI 300 «Strix» y las CPU para centros de datos EPYC «Turin» de quinta generación.

AMD acaba de comenzar con Zen 5, por lo que podemos esperar aún más productos en el futuro a medida que la compañía afina la arquitectura para PC y servidores.