Nemez, Fitzchens Fitz y HighYieldYT publicaron imágenes de alta resolución del CCD de 8 núcleos «Zen 5» de AMD, y que han sido anotadas por ellos. Estas imágenes ofrecen una vista detallada de cómo se ven el silicio y sus diversos componentes, en particular el nuevo núcleo de CPU «Zen 5» con su FPU de 512 bits. El paquete «Granite Ridge» se parece a «Raphael», con hasta dos matrices complejas de CPU de 8 núcleos (CCD) según el modelo de procesador y una matriz de E/S de cliente (cIOD) ubicada centralmente. Esta cIOD se ha trasladado de «Raphael», lo que minimiza los costes de desarrollo de productos para AMD al menos para la parte sin núcleo del procesador. El CCD «Zen 5» está construido sobre el nodo de fundición N4P (4 nm) de TSMC.

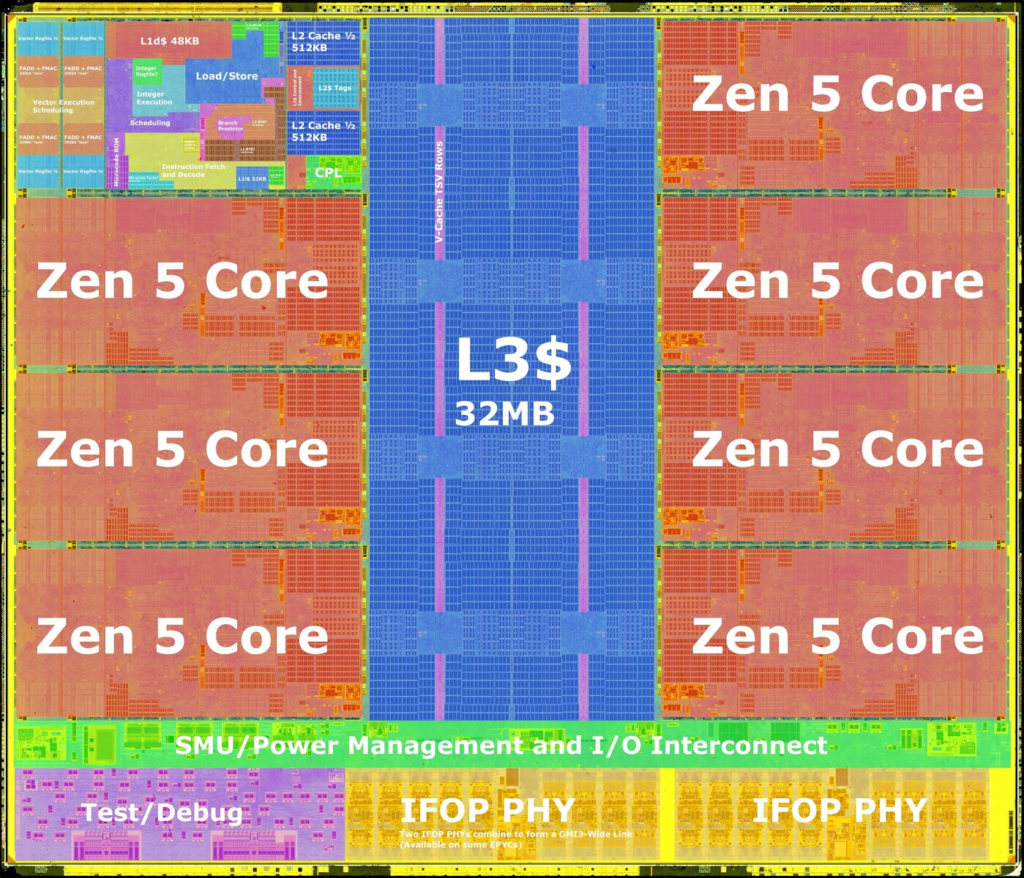

En el paquete «Granite Ridge» se ven hasta dos CCD «Zen 5» colocados más cerca uno del otro que los CCD «Zen 4» en «Raphael». En la imagen, se puede ver la almohadilla del CCD ausente detrás de la máscara de soldadura del sustrato de fibra de vidrio, cerca del CCD actual. El CCD contiene 8 núcleos de CPU «Zen 5» de tamaño completo, cada uno con 1 MB de caché L2 y una caché L3 de 32 MB ubicada centralmente que se comparte entre los ocho núcleos. Los únicos otros componentes son una SMU (unidad de administración del sistema) y los PHY Infinity Fabric over Package (IFoP), que conectan el CCD al cIOD.

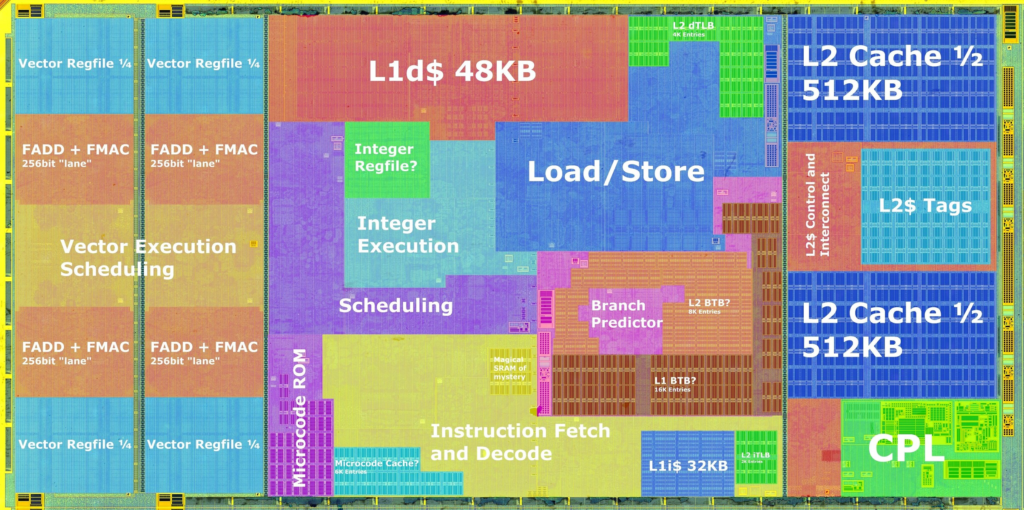

Cada núcleo de CPU «Zen 5» es físicamente más grande que el núcleo «Zen 4» (construido sobre el proceso TSMC N5), debido a su ruta de datos de punto flotante de 512 bits. El motor vectorial del núcleo se lleva hasta el borde mismo del núcleo. En el CCD, estos deberían ser los bordes del chip. Las FPU tienden a ser los componentes más activos en un núcleo de CPU, por lo que esto tiene sentido. El componente más interno (que mira hacia la caché L3 compartida) es la caché L2 de 1 MB. AMD ha duplicado el ancho de banda y la asociatividad de esta caché L2 de 1 MB en comparación con la del núcleo «Zen 4».

La región central del núcleo «Zen 5» tiene la caché L1I de 32 KB, la caché L1D de 48 KB, el motor de ejecución de enteros y el front-end muy importante del procesador, con su búsqueda y decodificación de instrucciones, la unidad de predicción de ramificaciones, la caché de microoperaciones y el programador.

La caché L3 integrada de 32 MB tiene filas de TSV (vías a través de silicio) que actúan como provisión para la caché V 3D apilada. La L3D (die de caché L3) de 64 MB se conecta con el bus de anillo del CCD mediante estas TSV, lo que hace que la caché V 3D de 64 MB sea contigua a la caché L3 integrada de 32 MB.

Por último, está la matriz de E/S del cliente (cIOD). No hay nada nuevo que informar aquí, el chip se ha heredado de «Raphael». Está construido sobre el nodo TSMC N6 (6 nm). Casi 1/3 del área de la matriz está ocupada por la iGPU y sus componentes aliados, como el motor de aceleración de medios y el motor de visualización. La iGPU se basa en la arquitectura gráfica RDNA 2 y tiene solo un procesador de grupo de trabajo (WGP), para dos unidades de cómputo (CU) o 128 procesadores de flujo. Otros componentes clave del cIOD son la interfaz PCIe Gen 5 de 28 carriles, los dos puertos IFoP para los CCD, un E/S SoC bastante grande que consta de USB 3.x y conectividad heredada, y el importante controlador de memoria DDR5 con su interfaz de memoria de doble canal (cuatro subcanales).

Os dejamos el video (no os lo podéis perder) «This is ZEN 5»